An FPGA is made to allow for simple reconfiguration by programmers, designers, or clients. Verilog HDL or VHDL (Hardware Description Language), the industry-standard language for programming FPGAs, is used to configure an FPGA in a particular configuration.

An FPGA is made up of a variety of reconfigurable interconnects that link logic gates for carrying out certain tasks, as well as programmable logic gates/blocks like AND, OR, XOR, NOT, memory elements, DSP components, etc.

FPGAs which are part of Embedded IC are therefore nothing more than logic blocks and interconnects that may be programmed to carry out various sophisticated tasks using Hardware Description Languages (Verilog HDL/VHDL). In fact, practically any DSP algorithm may be implemented using FPGAs. Some FPGAs also include embedded soft-core processors, such as the Nios II from Altera and the MicroBlaze from Xilinx, so that we may program the processor using C and C++ just like we would a microcontroller. Additionally, the soft processors can interact with hardware accelerators to accelerate complicated DSP operations, resulting in a more adaptable embedded system for specialized applications.

What is Verilog?

A text-based language called Verilog is used to describe electronic circuits and systems. Verilog is useful in designing electronic timing analysis, synthesis of logic, test analysis, and verification through simulation.

The IEEE standard Verilog HDL (number 1364) exists. The first iteration of the IEEE standard for Verilog was released in the year 1995. The majority of Verilog users utilize the upgraded version that was released in 2001. The Language Reference Manual, or LRM, is the name of the IEEE Verilog standard document. The Verilog HDL is defined in its whole and in this authorized definition.

What is VHDL?

The Hardware Description Lingualize (HDL) is used for designing digital circuits. VHSIC Hardware Description Language (VHDL), also known as VHDL. VHSIC is used for very high-speed integrated circuits.

The US defense department launched VHDL in the year 1981. The first version of VHDL was launched and released in 1985 in business collaboration with Texas Instrument and IBM. Xilinx created the first FPGA in 1984 and after that, VHDL was added as its product. After that, VHDL has been developed into a language for the design, simulation, and synthesis of digital circuits.

Verilog vs. VHDL

| VHDL | Verilog |

| Strongly typed | Weakly typed |

| Easier to understand | Less code to write |

| More simple in use | Types of hardware modeling language |

| Wordy | Succinct |

| Non-C-like syntax | Similarities to the C language |

| Variables described by data type | Programming constructs of lower level |

| Wide application for FPGAs and military | A better understanding on hardware modeling |

| More difficult to learn | Simpler to learn |

Conclusion of Verilog vs. VHDL

Strong typing is used in VHDL. The compiler prevents you from writing invalid code, therefore, VHDL is more difficult for beginners. On the other hand, weak typing is used in Verilog., and it enables you to write incorrect, but shorter code.

Verilog is much like C programming language, and those who have knowledge and proficiency in C can comprehend Verilog’s operation easily.

VHDL also necessitates a lot of typing. Less code to accomplish the same work is required in Verilog. VHDL is very deterministic while Verilog can be sometimes non-deterministic.

How does FPGA work?

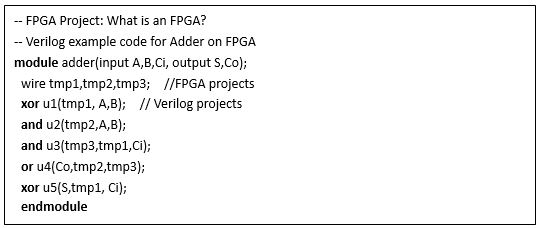

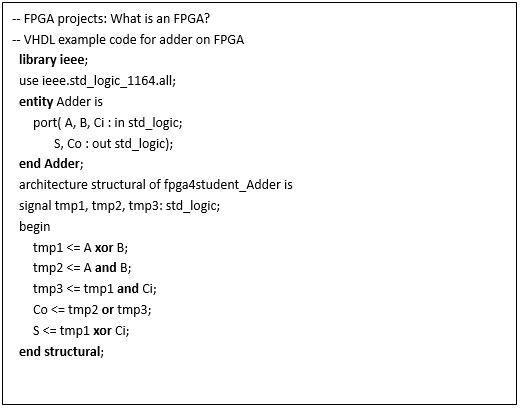

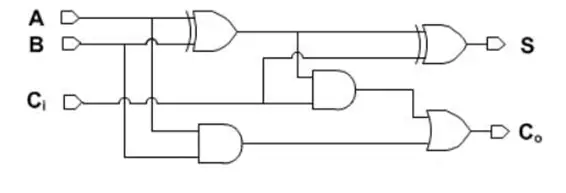

Now, we will take a simple example to understand how to use an FPGA. Suppose you have created a 1-bit full adder and derived its logic diagram shown in the below picture.

The above logic diagram of a 1-bit full adder is created on FPGA using logic gates XOR, AND, and OR. These logic gates used for a 1-bit full adder can be joined through either Verilog or VHDL to understand how the adder works on an FPGA.

Verilog code for the adder:

— Example- Verilog code for Adder on FPGA

module fpga4student_adder(input A,B,Ci, output S ,Co);

wire tmp1,tmp2,tmp3; //FPGA projects

xor u1(tmp1,A,B); // Verilog projects

and u2(tmp2,A,B);

and u3(tmp3,tmp1,Ci);

or u4(Co,tmp2,tmp3);

xor u5(S,tmp1,Ci);

end module

VHDL code for the adder:

— Example- VHDL code for adder on FPGA

library ieee;

use ieee.std_logic_1164.all;

entity fpga4student_Adder is

port( A, B, Ci : in std_logic;

S, Co: out std_logic);

end fpga4student_Adder;

architecture structural of fpga4student_Adder is

signal tmp1, tmp2, tmp3: std_logic;

begin

tmp1 <= A xor B;

tmp2 <= A and B;

tmp3 <= tmp1 and Ci;

Co <= tmp2 or tmp3;

S <= tmp1 xor Ci;

end structural;

Advantages of FPGA

Very fast on-chip demonstration:

The primary factor in my love of FPGA design is how quickly a design can be verified on an FPGA. With FPGA, everything is already set up; using a specific FPGA programming tool, we simply need to download the program file to the FPGA and observe how it functions there, whereas ASICs could take several months just for tape-out plus another lag for PCB design.

Programmable:

The most notable aspect of FPGA that we simply could not ignore is its programmability. FPGAs can be programmed at the hardware level, in contrast to ASICs or microcontrollers, which are fixed in terms of hardware (although they can be programmed at the software level). They can be programmed to execute practically any digital complicated functionality, and they can also be reconfigured as needed in the future.

Simple and fast design process:

The design process is quite straightforward to master and is another fantastic feature of FPGA. Since creating, verifying, and implementing an ASIC requires numerous intricate steps, the design cycle is exceedingly time-consuming and difficult. However, because FPGA is already a described and tested device, the FPGA design process typically eliminates complex and time-consuming processes like Floor-planning, Timing Analysis, Physical Implementation, etc.

Flexibility of FPGA:

Designers can create their own applications with FPGAs thanks to their increasing flexibility. As was already noted, FPGA suppliers offer their own soft processors, such as the MicroBlaze from Xilinx and the Nios II from Altera, to give designers additional flexibility throughout the design and programming processes. In fact, FPGA hardware accelerators with hardware-level reconfigurable capability (Verilog/VHDL) can be used for high-speed operations whereas soft processors with software-level reconfigurable capability (C, C++, etc.) can be used for low and average-speed applications.

High performance of FPGA:

High performance is a wonderful aspect of FPGA architecture. While processor-based ASICs or DSPs execute instructions sequentially, FPGAs take advantage of hardware parallelism to achieve ground-breaking performance for challenging designs. As a result, they offer faster implementations than processor-based ASICs. To accelerate processing time, digital signal processing methods can be implemented using the FPGA’s parallelism.